# DIMM-Base Board Design

**Application Note**

Rev6 / 07.05.2014

#### © Copyright 2012 emtrion GmbH

All rights reserved. This documentation may not be photocopied or recorded on any electronic media without written approval. The information contained in this documentation is subject to change without prior notice. We assume no liability for erroneous information or its consequences. Trademarks used from other companies refer exclusively to the products of those companies.

Revision: 6 / 07.05.2014

| Rev | Date/Signature | Changes                                                                                                                                                                                                                                                                                                                                                          |

|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 12.05.2011/Mt  | First revision                                                                                                                                                                                                                                                                                                                                                   |

| 2   | 11.11.2011/Mt  | <ul> <li>Added new possibility to switch between the LAN Transformer voltages</li> <li>Added SODIMM module fixing</li> <li>Changed mechanical connector placement drawing</li> <li>Changed processor module mechanical drawing (J4 orientation)</li> <li>Added periphery 3,3V and signal POWER_ON_BASE</li> <li>Added SODIMM connector recommendation</li> </ul> |

| 3   | 17.01.2012/Mt  | Added the second paragraph in chapter 1 Changed the FET T16 in the LAN power circuit in chapter 3.1                                                                                                                                                                                                                                                              |

| 4   | 12.04.2012/Mt  | Added the delayed RESI# feature                                                                                                                                                                                                                                                                                                                                  |

| 5   | 25.10.2012/Bue | CPU modules DIMM.EMEV2 and DIMM.AM335x added, several contents updated                                                                                                                                                                                                                                                                                           |

| 6   | 07.05.2014/Ko  | Updated Data for DIMM-MX6, DIMM-RZ, Cadun, Tarion                                                                                                                                                                                                                                                                                                                |

# **Table of Contents**

| 1 | Intr | oduction                                          | 4    |

|---|------|---------------------------------------------------|------|

| 2 | Fea  | tures                                             | 5    |

| 3 |      | cial circuits and differences between CPU modules |      |

|   | 3.1  | Ethernet                                          | 8    |

|   | 3.2  | USB Host VBUS Voltage                             | 9    |

|   | 3.3  | 3V3 supply for peripheral parts on Base board     |      |

|   | 3.4  | CPU-bus Interface                                 |      |

|   | 3.5  | Power Fail Warning, Reset Delay                   | . 11 |

|   | 3.6  | Extension connectors                              |      |

|   | 3.7  | Mechanical Characteristics                        | . 12 |

| 4 | Pin  | Assignments                                       | . 13 |

|   | 4.1  | SODIMM connector                                  | . 13 |

|   | 4.2  | SODIMM Extension Connector 1                      | . 17 |

|   | 4.3  | SODIMM Extension Connector 2                      | . 17 |

| 5 | Ref  | erences                                           | . 19 |

#### 1 Introduction

This Application Note helps baseboard development, if the baseboard shall be used with different Core modules. It helps to consider the differences if the developed baseboard shall be compatible for several DIMM modules.

This collection of data is based on our today's state of knowledge. Support for customer-specific Baseboards available on request.

The emtrion DIMM interface between the emtrion DIMM Core modules and the emtrion baseboards is an emtrion internal standardized interface. This standard defines the interfaces on the SODIMM connector.

This standard is supported by the Core modules

- DIMM-SH7723

- DIMM-SH7724

- DIMM-MX257

- DIMM-MX53x

- DIMM-MX6

- DIMM-EMEV2

- DIMM-AM335x

- DIMM-RZ

It is also supported by the carrier boards

- HiCO.DIMM-Base

- DIMM-Eco-Base Verno

- DIMM-Eco-Base Cadun

- DIMM-Eco-Base Tarion

- DIMM-Base Lothron

#### 2 Features

A couple of different DIMM Core modules are available from emtrion. Every Core module uses the SODIMM connector as the main interface. In general the Core modules are pin compatible, but not every module uses all interfaces, because they have sometimes different features. In the following table the Core modules features are listed.

The interfaces and features are described in more detail in the appropriate HW manuals of the modules. In this table only the general availability is shown.

| Feature                | DIMM-<br>SH7723 | DIMM-<br>SH7724 | DIMM-<br>MX257 | DIMM-<br>MX53x | DIMM-<br>EMEV2 | DIMM-<br>AM335x | DIMM-MX6 | DIMM-RZ |

|------------------------|-----------------|-----------------|----------------|----------------|----------------|-----------------|----------|---------|

| Ethernet               | Χ               | X               | Χ              | Χ              | Χ              | Χ               | Χ        | Χ       |

| USB Host               | Χ               | Χ               | Χ              | Χ              | Χ              | Χ               | Χ        | Χ       |

| USB Device             | Χ               | Χ               | X              | X              | Χ              | Χ               | Χ        | Χ       |

| TFT Display (generic)  | Χ               | Χ               | Χ              | Χ              | Χ              | Χ               | Χ        | Χ       |

| <b>Touch Screen</b>    | Χ               | Χ               | X              | Χ              | Χ              | Χ               | Χ        | Χ       |

| CMOS Camera Input<br>1 | Χ               | X               | -              | X              | Χ              | -               | Χ        | Х       |

| CMOS Camera Input<br>2 | -               | X               | -              | Χ              | -              | -               | X        | -       |

| Video Input            | Χ               | Χ               | -              | Χ              | Χ              | -               | Χ        | Χ       |

| Video Output           | Χ               | Χ               | -              | -              | Χ              | -               | -        | -       |

| Analog Audio (I2S)     | Χ               | Χ               | Χ              | Χ              | Χ              | Χ               | Χ        | Χ       |

| Digital Audio (SPDIF)  | Χ               | -               | -              | Χ              | -              | -               | Χ        | Χ       |

| SD-Card 1              | Χ               | Χ               | Χ              | Χ              | Χ              | Χ               | Χ        | Χ       |

| SD-Card 2              | Χ               | Χ               | Χ              | Χ              | Χ              | -               | Χ        | Χ       |

| UART_A (RS232)         | Χ               | X               | X              | Χ              | Χ              | Χ               | Х        | Χ       |

| UART_B (LVTTL)         | Χ               | X               | X              | Χ              | Χ              | Χ               | Χ        | Χ       |

| UART_C (LVTTL)         | Χ               | X               |                | Χ              | Χ              | Χ               | Х        | Χ       |

| UART_D (LVTTL)         | Χ               | Χ               | Χ              | Χ              | X              | Χ               | Χ        | X       |

| UART_E(LVTTL)            | Χ | Χ | Χ | Χ | - | (X) | Χ | Χ |

|--------------------------|---|---|---|---|---|-----|---|---|

| CAN1                     | - | Χ | Χ | Χ | Χ | Χ   | Χ | Χ |

| CAN2                     | - | - | Χ | Χ | - | (X) | Χ | Χ |

| SPI                      | Χ | Χ | Χ | Χ | Χ | Χ   | Χ | Χ |

| I <sup>2</sup> C         | Χ | Χ | Χ | Χ | Χ | Χ   | Χ | Χ |

| IrDA                     | Χ | Χ | Χ | Χ | - | -   | Χ | - |

| GPIO_0                   | Χ | Χ | Χ | Χ | Χ | Χ   | Χ | Χ |

| GPIO_1                   | Χ | Χ | Χ | Χ | Χ | Χ   | Χ | Χ |

| GPIO_2                   | Χ | Χ | X | Χ | Χ | Χ   | Χ | Χ |

| GPIO_3                   | Χ | Χ | X | Χ | Χ | X   | X | Χ |

| GPIO_4                   | Χ | Χ | - | Χ | Χ | Χ   | Χ | Χ |

| GPIO_5                   | Χ | Χ | X | Χ | Χ | X   | X | Χ |

| GPIO_6                   | Χ | Χ | - | Χ | Χ | Χ   | Χ | Χ |

| GPIO_7                   | Χ | Χ | X | Χ | Χ | X   | X | Χ |

| GPIO_8                   | Χ | Χ | X | - | Χ | Χ   | Χ | Χ |

| GPIO_9                   | Χ | Χ | X | - | Χ | X   | Χ | Χ |

| ANA_IN1                  | X | - | X | - | Χ | X   | - | Χ |

| ANA_IN2                  | X | - | Χ | - | X | X   | - | Χ |

| ANA_IN3                  | X | - | X | - | - | X   | - | Χ |

| ANA_IN4                  | Χ | - | Χ | - | - | X   | - | Χ |

| <b>CPU-Bus Interface</b> | X | - | Χ | X | Χ | -   | - | - |

| IRQ-A                    | X | Х | X | Χ | Χ | X   | X | X |

| IRQ-B                    | Χ | X | Χ | Χ | Χ | X   | Χ | X |

| NMI                      | X | Χ | X | Χ | Χ | X   | X | X |

| BAT                      | Χ | X | Χ | Χ | Χ | X   | Χ | X |

| RESI                     | X | Χ | X | X | X | X   | Χ | X |

| RESO                     | Χ | X | Χ | Χ | Χ | X   | Χ | X |

| DMA                      | - | Χ | - | - | - | -   | Χ | - |

| Extension connector 1    | - | Χ | - | X | X | -   | Χ | - |

| Extension connector 2    | - | - | - | X | - | -   | X | Χ |

| VOU_DEST                 | Χ | - | - | - | Χ | -   | - | - |

|                          |   |   |   |   |   |     |   |   |

| VOU_RST# | Χ | Χ | - | Χ | Χ | - | Χ   | Χ |

|----------|---|---|---|---|---|---|-----|---|

| VIO_RST# | Χ | Χ | Χ | Χ | Χ | - | Χ   | Χ |

| VIO_SRC  | Χ | Χ | Χ | Χ | Χ | - | Χ   | Χ |

| SATA     | - | - | - | Χ | - | - | Χ   | - |

| LVDS     | - | - | - | Χ | - | - | Χ   | Χ |

| KPP      | - | - | - | Χ | - | - | -   | - |

| miniPCle | - | - | - | - | - | - | (X) | - |

| HDMI     | - | - | - | - | - | - | (X) | - |

## **Symbol Explanation:**

X: feature or interface is fully supported

(X): availability depends on pin multiplexing

- This feature or interface is not supported

## 3 Special circuits and differences between CPU modules

Although the Core modules are pin compatible, there some little differences which must be considered at a Base board design if different modules shall be supported.

Also some special circuits will be explained in the following chapters.

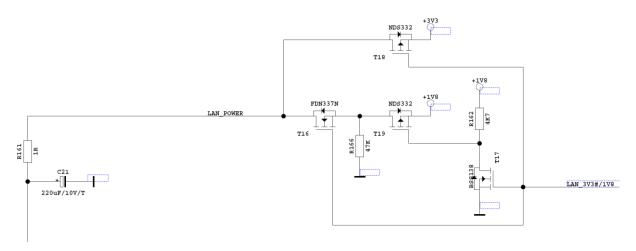

#### 3.1 Ethernet

The Core modules use different Ethernet Controllers. The Ethernet controllers demand different supply voltages for the transformer. Actually two different voltages are needed by different modules, 1.8 V and 3.3 V.

The following table shows the LAN transformer voltage of the CPU modules:

| CPU module  | LAN transformer voltage |

|-------------|-------------------------|

| DIMM-SH7723 | 1.8 V                   |

| DIMM-SH7724 | 3.3 V                   |

| DIMM-MX257  | 3.3 V                   |

| DIMM-MX53x  | 3.3 V                   |

| DIMM-MX6    | 3.3 V                   |

| DIMM-EMEV2  | 1.8 V                   |

| DIMM-Am335x | 3.3 V                   |

| DIMM-RZ     | 3.3 V                   |

If the baseboard shall be compatible for all DIMM Core modules, the LAN transformer voltage on the baseboard must be switchable between 3.3 V and 1.8 V. This can be done via a jumper or via resistors that are fit optionally.

The following circuit shows a third solution which enables the voltage to be switched by software.

LAN\_POWER will be 3,3V if the signal LAN\_3V3#/1V8 is low. LAN\_POWER will be 1,8V if the signal LAN\_3V3#/1V8 is high. The baseboard designer must set the default value of the signal LAN\_3V3#/1V8 via a resistor for example.

Actually voltage switching by software is not supported by the CPU modules.

To be more robust against mechanical stress the CPU module should be fixed with screws. Two mounting holes at the opposite edge of the SODIMM connector are provided. The mounting holes vary between the CPU modules according to upper table. Also the hole diameters vary between the Base boards from emtrion.

To use M2x8 screws and 3mm high plastic spacers between the CPU module and the Base board fits for all boards.

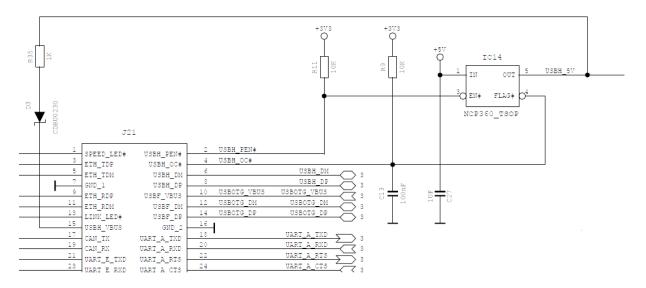

#### 3.2 USB Host VBUS Voltage

The use of pin 15 of the SODIMM connector was changed from 3V3 supply to USB Host VBUS. This was necessary because some newer CPUs demand to watch the USB Host VBUS signal.

To be compatible to all CPU modules the following circuit should be realized on the Base board:

The VBUS output voltage of the USB Host interface on the Base board is connected to pin 15 of the SODIMM connector by a small schottky diode and a 1k series resistor. This circuit conforms to all CPU modules.

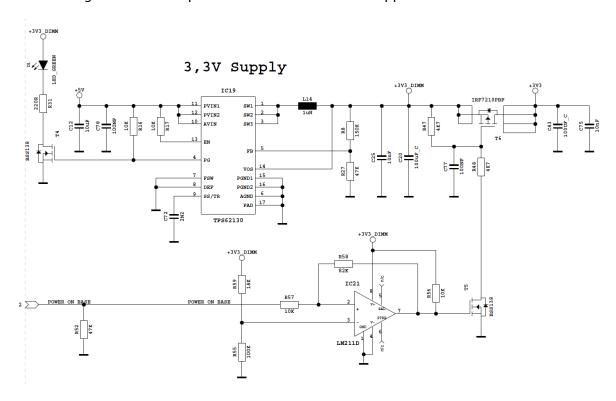

#### 3.3 3V3 supply for peripheral parts on Base board

The use of pin 135 of the SODIMM connector was changed from 3V3 supply to signal POWER\_ON\_BASE. This was necessary because some newer CPUs demand that during the power on sequence the 3.3 V supply is switched on at the end. If peripheral parts on the Base board are

powered from the beginning a current flow from the I/O pins into unpowered areas of the CPU might cause problems.

The 3.3 V power supply pins at the SODIMM connector are only used to supply the CPU module. The 3.3 V supply of the peripheral parts on the Base board must be separated from it. The signal POWER\_ON\_BASE is provided to control the separated power supply by the CPU module. A high level switches the supply of the peripherals on the Base board on.

The following circuit shows a possible solution for the 3.3 V supplies:

The 3.3 V supply +3V3\_DIMM is connected to the SODIMM connector. The local peripheral supply +3V3 is separated by the P-MOSFET T6 which is driven by the comparator IC21 and the N-MOSFET T5. The comparator is used since the falling slope of the signal POWER\_ON\_BASE is very slow on some CPU boards. The comparator ensures hard switching at power on and off.

According to the Base boards needs the above circuit around T6 can also be replaced by an integrated high side switch.

#### 3.4 CPU-bus Interface

The characteristics of the CPU-bus interface are CPU board specific. While DIMM-SH7724 even supports DMA transfers DIMM-Am335x does not have a bus interface at all.

More details about the characteristics of the interface can be found in the HW manual of the CPU modules.

If necessary ask emtrion for further support.

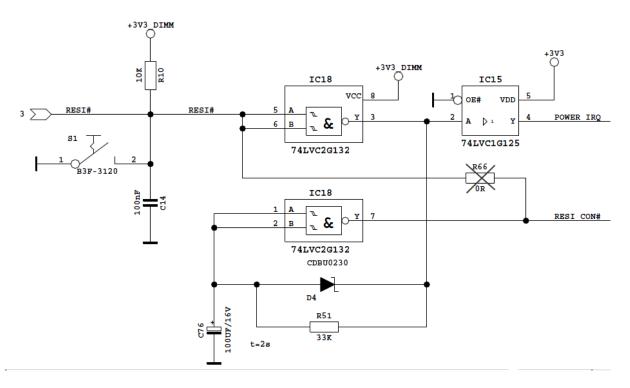

#### 3.5 Power Fail Warning, Reset Delay

Some operating systems, like Android, demand that the CPU closes the file system before it is stopped. Otherwise the system might be corrupted at the next start. Such critical stops can be caused by an unexpected power fail or simply by pressing the reset button during operation.

To avoid system corruptions the CPU should get an early power fail warning or the information that a reset will follow within a short time.

An example how a reset warning can be realized is shown in the following circuit:

In this circuit the signal POWER\_IRQ is driven high immediately if the reset button S1 is pressed or the signal RESI# becomes low. If R66 is not fit the rising edge of POWER\_IRQ is delayed by the circuit comprised of R51, C76 and D4 and causes an active low reset signal RESI\_CON# some time later. The delay between POWER\_IRQ and RESI\_CON# becoming active can be used by the software to close the necessary tasks.

The above circuit is realized on the Base board DIMM-Eco-Base Verno. The values of R51 and C76 must be adapted to the software demands. The signal POWER\_IRQ is connected to IRQB of the SODIMM connector.

Watch that the reset button must be pressed as long as given delay time before a reset happens.

#### 3.6 Extension connectors

Some CPUs are rich of interfaces that are not provided at the SODIMM connector. Within these are  $2^{nd}$  camera interface, LVDS display output, SATA interface and others.

To give access to these additional interfaces two extension were added. The pin usage if described in the following chapter.

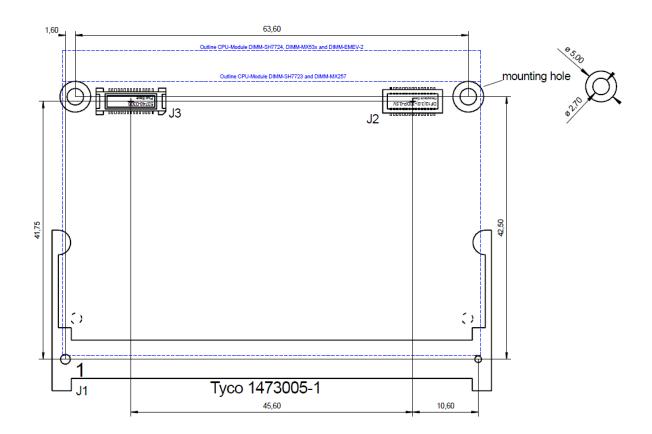

#### 3.7 Mechanical Characteristics

Some of the CPU modules have one or two extension connectors which incorporate additional interfaces that are not available at the SODIMM connector. These modules are wider than the other modules.

The Base board should provide enough space if various CPU modules shall be supported. The following table shows the dimensions of the CPU modules:

| CPU module  | Dimensions    | Mounting Hole Diameter |

|-------------|---------------|------------------------|

| DIMM-SH7723 | 67,6mm x 45mm | 2.8 mm                 |

| DIMM-SH7724 | 67,6mm x 50mm | 2.8 mm                 |

| DIMM-MX257  | 67,6mm x 45mm | 2.5 mm                 |

| DIMM-MX53x  | 67,6mm x 50mm | 2.8 mm                 |

| DIMM-MX6    | 67,6mm x 50mm | 2.8 mm                 |

| DIMM-EMEV2  | 67,6mm x 50mm | 2.8 mm                 |

| DIMM-Am335x | 67,6mm x 45mm | 2.2 mm                 |

| DIMM-RZ     | 67,6mm x 45mm | 2.8 mm                 |

Watch that even if the interfaces at the extension connectors shall not be used on a Base board no other parts should be located at the position of the connectors. Otherwise if the CPU board is changed later its extension connectors might conflict with the parts.

The following drawing shows the mechanical position of the extension connectors on the baseboard.

Watch: This drawing is only valid when the specified connector types are used!!

The complete drawing can be found on the emtrion support homepage:

http://www.support.emtrion.de/doku.php?id=hw:baseboards hicodimm

# 4 Pin Assignments

#### 4.1 SODIMM connector

Type 200 pin SODIMM socket, 0.6 mm Pitch, 2,5V keying

| Pin | Signal     | Inte     | rface         | Signal    | Pin |

|-----|------------|----------|---------------|-----------|-----|

| 1   | SPEED_LED# |          |               | USBH_PEN# | 2   |

| 3   | ETH_TDP    | Ethernet | Host          | USBH_OC#  | 4   |

| 5   | ETH_TDM    |          | USB           | USBH_DM   | 6   |

| 7   | GND        |          |               | USBH_DP   | 8   |

| 9   | ETH_RDP    |          | SB<br>rice    | USBF_VBUS | 10  |

| 11  | ETH_RDM    |          | USB<br>Device | USBF_DM   | 12  |

| 13 | LINK_LED#   |          |              | USBF_DP     | 14 |

|----|-------------|----------|--------------|-------------|----|

| 15 | USBH_VBUS   | USB Host | Power        | GND         | 16 |

| 17 | CAN_TX      | CAN      |              | UART-A_TXD# | 18 |

| 19 | CAN_RX      |          |              | UART-A_RXD# | 20 |

| 21 | UART-E_TXD  | UART-E   | UART-A       | UART-A_RTS# | 22 |

| 23 | UART-E _RXD |          |              | UART-A_CTS# | 24 |

| 25 | UART-D_TXD  |          |              | Touch_XP    | 26 |

| 27 | UART-D_RXD  | UART-D   | <del>.</del> | Touch_XM    | 28 |

| 29 | UART-C_TXD  | _        | Touch        | Touch_YP    | 30 |

| 31 | UART-C_RXD  | UART-C   |              | Touch_YM    | 32 |

| 33 | UART-B_TXD  |          |              | ANA1        | 34 |

| 35 | UART-B_RXD  | UART-B   | A/D          | ANA2        | 36 |

| 37 | ANA4        | A/D      |              | ANA3        | 38 |

| 39 | +3V3        | Pov      | wer          | GND         | 40 |

| 41 | LCD_D22     |          |              | LCD_D23     | 42 |

| 43 | LCD_D20     |          |              | LCD_D21     | 44 |

| 45 | LCD_D18     |          |              | LCD_D19     | 46 |

| 47 | LCD_D16     |          |              | LCD_D17     | 48 |

| 49 | LCD_D14     |          |              | LCD_D15     | 50 |

| 51 | LCD_D12     |          | 3            | LCD_D13     | 52 |

| 53 | LCD_D10     |          | ĭ            | LCD_D11     | 54 |

| 55 | LCD_D8      |          |              | LCD_D9      | 56 |

| 57 | LCD_D6      |          |              | LCD_D7      | 58 |

| 59 | LCD_D4      |          |              | LCD_D5      | 60 |

| 61 | LCD_D2      |          |              | LCD_D3      | 62 |

| 63 | LCD_D0      |          |              | LCD_D1      | 64 |

| 65 | +3V3        | Por      | wer          | GND         | 66 |

| 67 | LCDRD#      |          |              | LCD_LCLK    | 68 |

| 69 | LCD_DISP    |          | 3            | LCD_DCK     | 70 |

| 71 | LCD_HSYN    | -        | -            | LCD_DON     | 72 |

| 73 | LCD_VSYN    |          |              | LCD_VCPWC   | 74 |

| 131<br>133 | GPIO2<br>GPIO0      |       |           | GPIO3<br>GPIO1     | 132<br>134 |

|------------|---------------------|-------|-----------|--------------------|------------|

| 129        |                     |       | 5         | GPIO3              | 130        |

| 127        | GPIO6               |       | 2         | GPIO7              | 128        |

|            | GPIO8               |       |           | GPIO9              | 126        |

|            | GND                 | Power |           | AUDIO_MCLK         | 124        |

| 121        | SPDO                |       |           | AUDIO_DATO         | 122        |

| 119        | SPDI                | SPDIF | Audio     | AUDIO_DATI         | 120        |

|            | SDA                 |       | <u>.e</u> | AUDIO_LRC          | 118        |

| 115        |                     | 12C   |           | AUDIO_BCK          | 116        |

| 113        | SPI_SCK             |       |           | SPI_MOSI           | 114        |

| 111        | SPI_SS#             | S     | PI        | SPI_MISO           | 112        |

| 109        | SDC2_WP#            |       | <u> </u>  | SDC1_WP#           | 110        |

| 107        | SDC2_CD#            |       | SD        | SDC1_CD#           | 108        |

| 105        | SDC2_CLK            |       |           | SDC1_CLK           | 106        |

| 103        | SDC2_CMD            | SDC2  |           | SDC1_CMD           | 104        |

| 101        | SDC2_D3             |       | SDC1      | SDC1_D3            | 102        |

| 99         | SDC2_D2             |       |           | SDC1_D2            | 100        |

| 97         | SDC2_D1             |       |           | SDC1_D1            | 98         |

| 95         | SDC2_D0             |       |           | SDC1_D0            | 96         |

| 93         | +3V3                | Pov   | wer       | GND                | 94         |

| 91         | VIO_RST#            |       |           | VIO0_D0            | 92         |

| 89         | VIO_SRC             |       |           | VIO0_D1            | 90         |

| 87         | VIO0_VD             |       | 5         | VIO0_D2            | 88         |

| 85         | VIO0_HD             |       |           | VIO0_D3            | 86         |

| 83         | VIO0_CLK            |       |           | VIO0_D4            | 84         |

| 81         | VIO0_FLD<br>VIO_CKO |       |           | VIO0_D6            | 82         |

| 77<br>79   | VOU_RST#            |       |           | VIO0_D7<br>VIO0_D6 | 78<br>80   |

| 75         | VOU_DEST            |       |           | LCD_VEPWC          | 76         |

|            | CS#        |             | IOIS16#    | 198        |

|------------|------------|-------------|------------|------------|

| 197        |            |             | 101616#    |            |

| 195        | WAIT#      |             | CE2B#      | 196        |

| 193        | ICIOWR#    |             | CE1B#      | 194        |

| 191        | ICIORD#    | Δ           | RESI#      | 192        |

| 189        | WE1#       | Bus Control | RESO#      | 190        |

| 187        | WE0#       | )<br>ntrc   | NMI        | 188        |

| 185        | RD/WR#     | _           | IRQ_B      | 186        |

| 183        | RD#        |             | IRQ_A      | 184        |

| 181        | BS#        |             | DACK       | 182        |

| 179        | CKIO       |             | DREQ       | 180        |

| 177        | D0         |             | D1         | 178        |

| 175        | D2         |             | D3         | 176        |

| 173        | D4         | Dat         | D5         | 174        |

| 171        | D6         | a D['       | D7         | 172        |

| 169        | D8         | <b>[0</b> ] | D9         | 170        |

| 167        | D10        |             | D11        | 168        |

| 163<br>165 | D14<br>D12 |             | D15        | 164<br>166 |

| 161        | +3V3       | Power       | GND<br>D15 | 162        |

|            |            | Power       |            |            |

| 159        | A0         |             | A1         | 160        |

| 155<br>157 | A4<br>A2   |             | A3         | 156        |

| 153        | A6         |             | A7<br>A5   | 154<br>156 |

| 151        | A8         |             | A9         | 152        |

| 149        | A10        |             | A11        | 150        |

| 147        | A12        |             | A13        | 148        |

| 145        | A14        |             | A15        | 146        |

| 143        | A16        |             | A17        | 144        |

| 141        | A18        |             | A19        | 142        |

| 139        | A20        |             | A21        | 140        |

#### 4.2 **SODIMM Extension Connector 1**

Type: 30-pin Header on Base: Hirose DF12(3.0)-30DP-0.5V 30-pin Receptacle on CPU module: Hirose DF12(3.0)-30DS-0.5V

| Pin | Signal    | Pin | Signal   |

|-----|-----------|-----|----------|

| 1   | GND       | 2   | +3.3 V   |

| 3   | VOU_D7    | 4   | VIO1_D7  |

| 5   | VOU_D6    | 6   | VIO1_D6  |

| 7   | VOU_D5    | 8   | VIO1_D5  |

| 9   | VOU_D4    | 10  | VIO1_D4  |

| 11  | VOU_D3    | 12  | VIO1_D3  |

| 13  | VOU_D2    | 14  | VIO1_D2  |

| 15  | VOU_D1    | 16  | VIO1_D1  |

| 17  | VOU_D0    | 18  | VIO1_D0  |

| 19  | GND       | 20  | GND      |

| 21  | VOU_CLKI  | 22  | VIO1_CLK |

| 23  | VOU_CLK   | 24  | VIO1_FLD |

| 25  | VOU_VSYNC | 26  | VIO1_VD  |

| 27  | VOU_HSYNC | 28  | VIO1_HD  |

| 29  | GND       | 30  | +3.3 V   |

### 4.3 **SODIMM Extension Connector 2**

Type 30-pin Header on Base: Molex 537480308 30-pin Receptacle on CPU module: Molex 529910308

| Pin | Signal   | Pin | Signal     |

|-----|----------|-----|------------|

| 1   | SATA_RXN | 2   | LVDS_TX2_N |

| 3   | SATA_RXP | 4   | LVDS_TX2_P |

| 5   | SATA_TXP | 6   | LVDS_TX0_N |

| 7   | SATA_TXN | 8   | LVDS_TX0_P |

embedded systems

| 9  | GND                             | 10 | GND        |

|----|---------------------------------|----|------------|

| 11 | KPP_ROW1/HDMI_D2_P              | 10 | LVDS_TX1_N |

| 13 | KPP_COL1/HDMI_D2_N              | 10 | LVDS_TX1_P |

| 15 | KPP_ROW0/HDMI_D1_P/PCIE_RXP     | 10 | GND        |

| 17 | KPP_COL0/HDMI_D1_N/PCIE_RXM     | 18 | LVDS_CLK_N |

| 19 | KPP_ROW2/HDMI_D0_P/PCIE_TXM     | 20 | LVDS_CLK_P |

| 21 | KPP_ROW3/HDMI_D0_N/PCIE_TXP     | 22 | GND        |

| 23 | KPP_COL3/HDMI_CLK_P/PCIE_CLK1_P | 24 | LVDS_TX3_N |

| 25 | KPP_COL2/HDMI_CLK_N/PCIE_CLK1_N | 26 | LVDS_TX3_P |

| 27 | HDMI_SCL                        | 28 | GND        |

| 29 | HDMI_SDA                        | 30 | HDMI_HPD   |

# **5** References

[1] DDR1 & DDR2 SODIMM Socket 0.6 mm Pitch 200 Pos Standard Profile Standard Type Tyco Electronics Part Number: 1473005-1